#### TC2

# Design for Power Gating — and what UPF can and cannot do for you

David Flynn

<u>David.Flynn@arm.com</u> – ARM Fellow, R&D

<u>David.Flynn@ecs.soton.ac.uk</u> – Visiting Professor

# Purpose of this user session ARM

#### Propose a basic "best practice" for power gating:

- Now that Synopsys EDA tools are fully multi-voltage aware...

- ... and Unified Power Format, UPF1.0, 'power intent' support is in place

#### Need to understand how

- UPF infers enhancements onto verified 'golden RTL' And therefore

- Develop a disciplined sub-set of UPF constructs and understand the interaction with RTL design

- notably clocks, resets and retention state

#### Outline

- 1. The basics of power gating for the RTL designer

- 2. UPF "intent" for power gating and interface clamping

- 3. Practical power gating for safe turn-on and testability

- 4. The problems managing resets, clocks/clock gating

- 5. Complications of state retention with power gating

- 6. Bringing it all together with a worked example

- 7. Conclusions

- Best-practice approaches

- Pitfalls to avoid.

# Power gating basics

- Given that product "standby" life is critical to many designs, especially where battery powered...

- ... and that at 90nm and below, CMOS technology leakage power grows in significance

- Power Gating is one key leakage mitigation technique

- "MTCMOS" introduces (High-Vth) transistor switches in series with the power rail(s) with conventional circuits (built up of one or more High/Standard/Low Vth cells)

- But introduces the complication that outputs float/collapse when the circuit is power gated off

- And register state of course is lost, so will need reinitializing or saving and restoring...

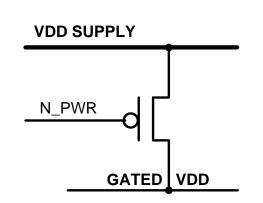

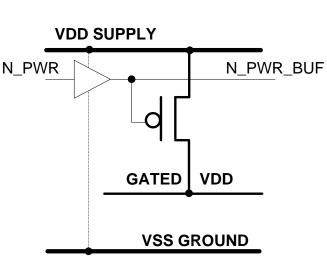

### Power gates

- Power gates are high-current transistor switches placed in series with the standard power supply or ground.

- "Header" PMOS switches shown

- Basic un-buffered switch

- Internally buffered switch

- "Footer" NMOS switch alternatives

- Unbuffered/buffered switches to VSS

- Typically many switches in parallel

Good "off" leakage but "on" IR drop

### **UPF** and Power gates

```

create power domain TOP

VDD SUPPLY

create power domain PD -elements { uBlock }

create supply port VDD -domain TOP

N_PWR

create supply net VDD -domain TOP

connect supply net VDD -ports VDD

GATED | VDD

create supply port VSS -domain TOP

create supply net

VSS -domain TOP

connect supply net VSS -ports VSS

VDD SUPPLY

create supply net

VDD SW -domain PD -resolve parallel

N PWR BUF

VSS -domain PD -reuse

create supply net

set domain supply net TOP -primary power net VDD -primary ground net VSS

set domain supply net PD -primary power net VDD SW -primary ground net VSS

GATED | VDD

create power switch PG -domain PD \

-input supply port {VDD VDD } -output_supply_port {VDD_SW VDD_SW_}_\

-control port {N PWR N PWR } -on state {on state VDD {!N PWR }}

map power switch PG -domain PD -lib cell HEADBUF16 X1M A12TL

```

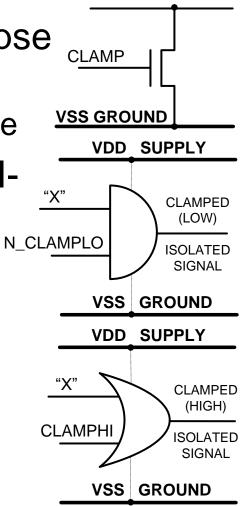

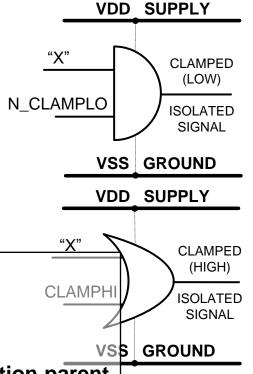

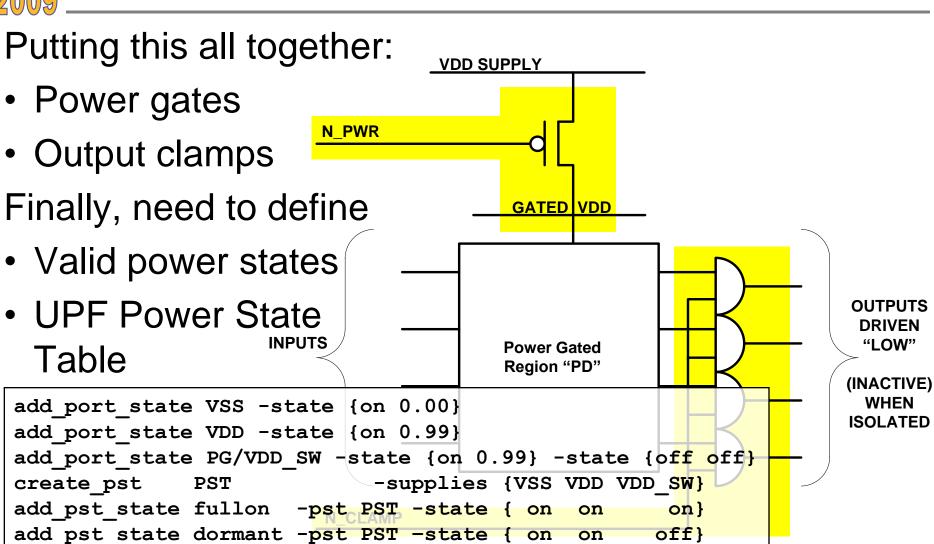

# **Output Clamping**

- Outputs of power-gated blocks collapse

- To a voltage where leakage through off switch is equal to residual circuit leakage

- For header switched systems a "pulldown" transistor is the minimum

- To avoid "multiple" driver issues special CLAMP cells are introduced to protect downstream inputs. e.g.

- CLAMPLO (AND-style function)

- CLAMPHI (OR-style function)

# **UPF** and Output Clamping

- For protocol-sensitive output signals the clamped values need to be architected

- No longer in the RTL

- An example of where UPF changes may break system verification

- UPF standard chooses isolation as the name for output clamping

```

set_isolation vsoc -domain PD -isolation_power_net VDD \

-isolation_ground_net VSS \

-clamp_value 0 -applies_to outputs

set_isolation_control vsoc -domain PD \

-isolation_signal N_CLAMPLO -isolation_sense low -location parent

```

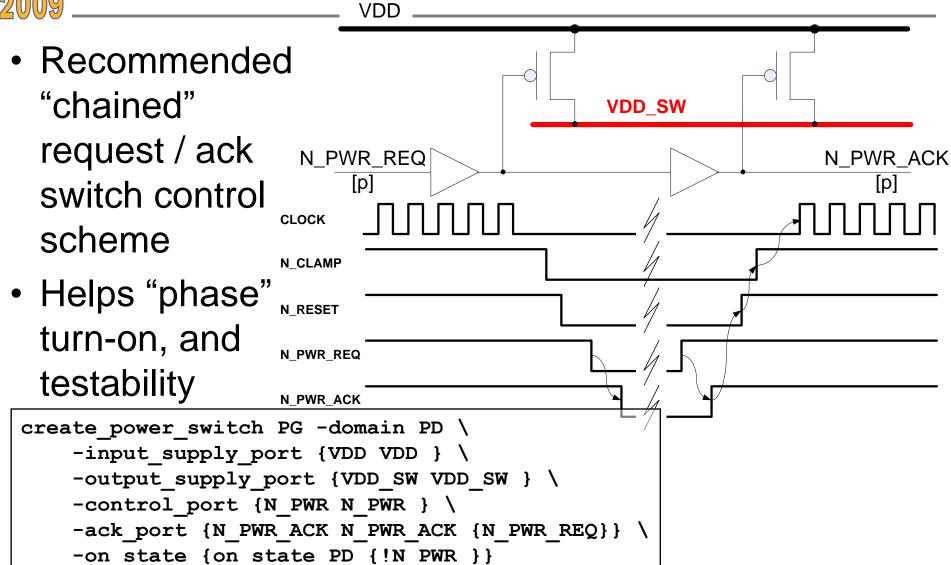

# UPF & Power Gating chains ARM

# RTL+ UPF power gating

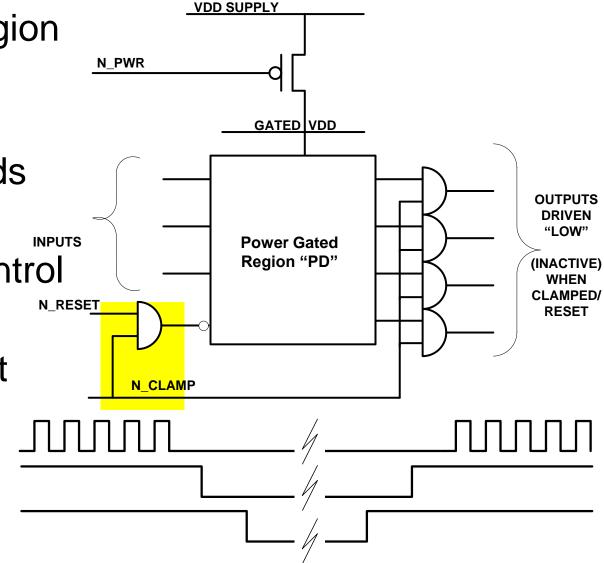

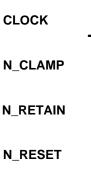

#### **UPF** and Resets

- A power gated region loses state

- Reset sequence required afterwards

- Ideally explicit individual RTL control

**CLOCK**

N\_CLAMP N\_RESET

N PWR

- "N\_CLAMP" on asynch reset input needs care

- i.e. separate

UPF clamps

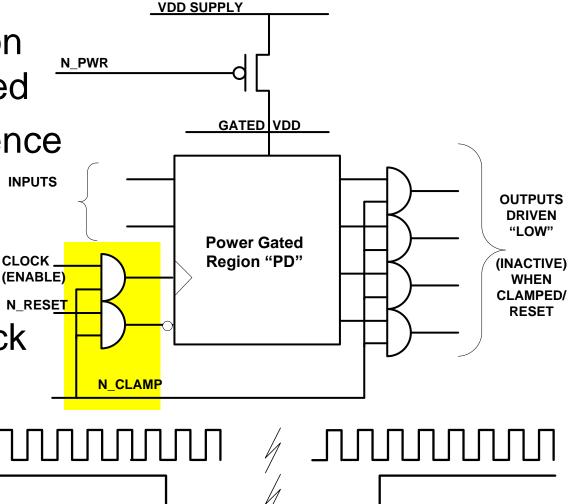

#### **UPF** and Clocks

A power gated region should not be clocked

Inhibit/enable sequence needs design/verify

CLOCK

Explicit RTL control ideally

• "N CLAMP" on clock enable needs (even more) care!

**CLOCK**

N PWR

**CLKENABLE** N CLAMP N RESET

#### **UPF** and State Retention

- UPF allows highly flexible (and dangerous) inference

- of retained state

- Safe options are:

- ALL state

- or NO state!

- Validation is key

- As well as from reset (easy!)

- Need to verify all pathological non-reset state interaction

- To prove no deadlock etc.

- Clock gates as well

- Explicit or inferred

```

map_retention_cell RET -domain PD \

-lib_cell_type RLAT \

-elements { . . . }

```

```

set_retention RET -domain PD \

-retention_power_net VDD \

-retention_ground_net VSS

set_retention_control RET -domain PD \

-save_signal {N_RETAIN low}

-restore_signal {N_RETAIN high}

map_retention_cell RET -domain PD \

-lib cell type DRFF

```

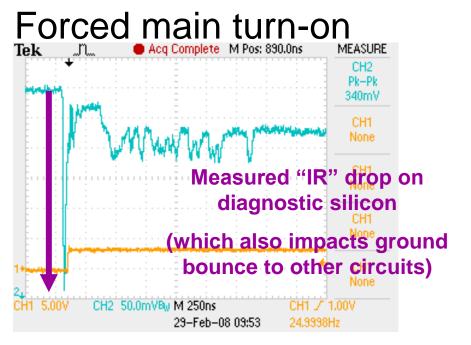

# **SRPG** Sequencing

SRPG

needs

explicit

RTL control

CLOCK

**N\_CLAMP**

**SAVE**

N RESET

**RESTORE**

N PWR

Depends

on the RET

FLOP style

Library

N PWR

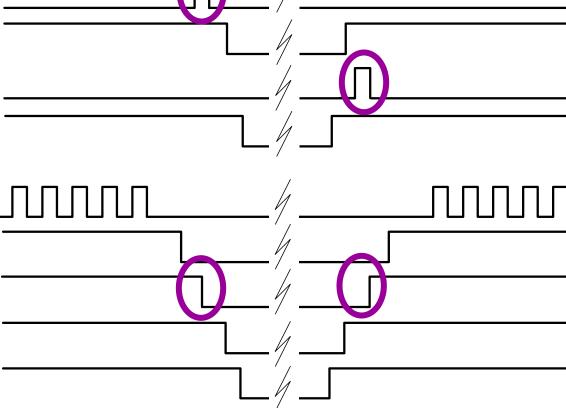

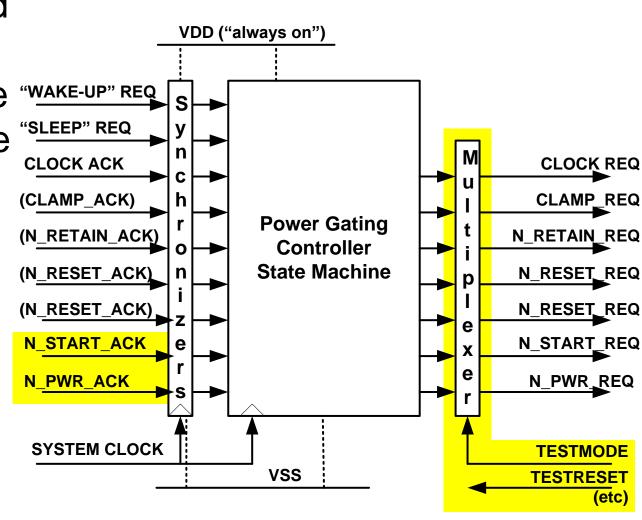

### SRPG controller

- RTL coded state machine

- Explicit drives to the UPF and RTL subsystem ports

- And to clock and reset controller

- For design-reuse across generations consider generic asynch handshakes

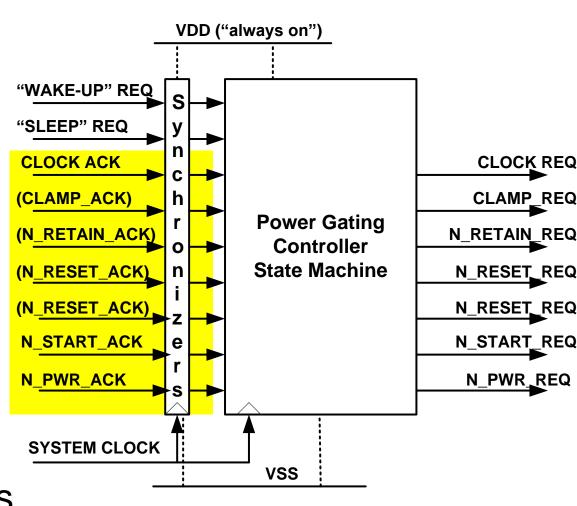

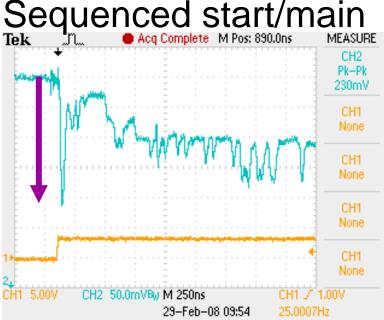

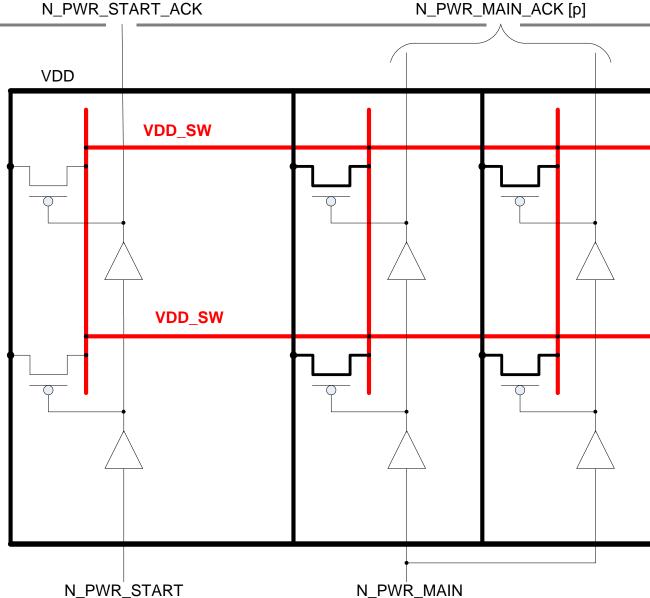

# Multiple Power-Gate chains A

- In order to safely avoid large power transients when turning on power gated regions consider "weak" and "strong" power gate chains (inferred in UPF)

- Measured benefits for TSMC 90nm G "SALT1" silicon

### Do not forget testability

- Well understood that Clocks and resets are made RTL controllable

- Same true for retention and power gating controls

- PG "ACK"

chains allow

buffer chain

integrity testing

# Multi-chain virtual power grid

- When using distributed power gating need to ensure good switched rail grid

- Ensure good current sharing across switches

- Suit "soft start"

## Conclusions – PG/UPF

- UPF can infer basic power gating, but design-time analysis is required to factor in appropriate power-up control strategies

- UPF infers basic interface output clamping in a straightforward manner but the designer needs to "architect" and specify the quiescent/safe values to be used

- How fast a power gated network can be turned-on requires attention to both the UPF inferred power gating structures and the RTL controller design

- Designing in handshake protocols across the UPF and RTL divide can facilitate design reuse and technology portability

- Power gating is not instantaneous or as transparent as clockgating. Clocks cannot be restarted until power rails are safely stabilized and valid. Resets can either be handled explicitly or require careful asserting with UPF-inferred input clamping.

# Conclusions – SRPG/UPF

- Arbitrary state retention inference through UPF is strongly to be discouraged

- For legacy IP, 'total state' or no state retention are the options that will verify and work

- UPF state integrity relies on not being compromised by power-gating switch-on transients

- Not only of the block in question but neighboring blocks on the SOC that share a common ground or power rail

- Single-edge clocking is strongly advocated otherwise clock gating constructs will have to infer retention latches for functional clock gating.

#### Questions?

#### Thank You

#### With thanks also to

- Alan Gibbons, Synopsys Inc, Reading UK

- John Biggs, James Myers, ARM Ltd, Cambridge UK

- Sachin Idgunji, Leah Schuth, ARM Inc, San Jose

- Electronics and Computer Science faculty Southampton University, UK